# 3D integration of 2D electronics

Darsith Jayachandran<sup>1,5</sup> ⋈, Najam U Sakib¹ & Saptarshi Das **©** <sup>1,2,3,4</sup> ⋈

#### **Abstract**

The adoption of three-dimensional (3D) integration has revolutionized NAND flash memory technology, and a similar transformative potential exists for logic circuits, by stacking transistors into the third dimension. This pivotal shift towards 3D integration of logic arrives on the heels of substantial improvements in silicon device structures and their subsequent scaling in size and performance. Yet, advanced scaling requires ultrathin semiconducting channels, which are difficult to achieve using silicon. In this context, field-effect transistors based on two-dimensional (2D) semiconductors have drawn notable attention owing to their atomically thin nature and impressive performance milestones. In addition, 2D materials offer a broader spectrum of functionalities – such as optical, chemical and biological sensing – that extends their utility beyond simple 'more Moore' dimensional scaling and enables the development of 'more than Moore' technologies. Thus, 3D integration of 2D electronics could bring us unanticipated discoveries, leading to sustainable and energy-efficient computing systems. In this Review, we explore the progress, challenges and future opportunities for 3D integration of 2D electronics.

### **Sections**

Introduction

Towards very-large-scale integration of 2D electronics

3D integration of 2D electronics

Design considerations and challenges

Conclusion

<sup>1</sup>Department of Engineering Science and Mechanics, The Pennsylvania State University, University Park, PA, USA. <sup>2</sup>Department of Electrical Engineering, The Pennsylvania State University, University Park, PA, USA. <sup>3</sup>Department of Materials Science and Engineering, The Pennsylvania State University, University Park, PA, USA. <sup>4</sup>Materials Research Institute, The Pennsylvania State University, University Park, PA, USA. <sup>5</sup>Present address: IBM Research, Albany, NY, USA. <sup>6</sup>Present address: IBM Research, Albany, NY, USA. <sup>7</sup>Present address: IBM Research, Albany, NY, USA. <sup>8</sup>Present address: IBM R

### **Key points**

- 2D electronics must overcome several challenges before they can be adopted in commercial semiconductor chips. Some of the major challenges are discussed in the section 'Towards very-large-scale integration of 2D electronics'.

- Research efforts in 2D material synthesis and device integration strategies must happen synergistically, with the goal of 3D integration, because silicon technology is already mature, with the most advanced nodes reaching the limits of planar integration in gate-all-around field-effect transistors.

- 3D integration with 2D electronics not only demands the maturity of 2D electronics in the planar dimension but also poses new difficulties in the vertical direction. These difficulties must be thoroughly understood and addressed before 2D materials can be introduced into commercial electronics.

- 2D materials have the potential to enable multifunctional chips by combining logic with memory and sensing in a 3D-integrated chip.

Multifunctional chips containing 2D electronics should be developed with the goal of manufacturing task-specific semiconductor chips and thereby addressing various integration challenges.

### Introduction

The unification of metal-oxide-semiconductor field-effect transistors (MOSFETs) with the concept of universal Turing machines in modern computer science marked a substantial milestone in the advance of digital electronics and technology. The desire to minimize the size and power requirements of computers demanded faster and more compact electronic circuits<sup>1</sup>. Moreover, Gordon Moore's prediction that the number of transistors on a chip would double approximately every two years spurred semiconductor industries to compete in a race to adhere to this trend, known as Moore's law<sup>2</sup>. This marked the beginning of an era dedicated to achieving maximal scaling in size and power efficiency of semiconductor chips, with the number of transistors per chip escalating from a few thousand to billions in less than five decades<sup>3</sup>. At present, scaling in semiconductor technology encompasses two primary aspects: (1) scaling based on system-level integration to augment the transistor count per chip and to incorporate additional functionalities into a system-on-a-chip and (2) scaling focused on the individual dimensions, structure and density of transistors4.

To facilitate scaling based on system-level integration, several semiconductor industries have developed various 3D integrated circuit (IC) packaging techniques<sup>5</sup> and integration solutions<sup>6</sup>, such as Intel's Foveros technology<sup>7</sup> and TSMC's 3DFabric, which utilize system-on-integrated-chips technology<sup>8</sup>. This arena of scaling thrives on innovations in technologies like wire bonding, through-silicon vias, through-glass vias, face-to-face chip stacking, flip-chip and the ThruChip interface<sup>9</sup>. These technologies enable increased interconnect bandwidth, enhanced performance, power and area, and potentially reduced costs, especially when stacking chiplets<sup>10</sup>. Conversely, the International Roadmap for Devices and Systems predicts that future process nodes will require highly parallel 3D architectures, achievable only through the sequential stacking of individual devices on top of one another<sup>11</sup>. Note that the term 'node' is not used to refer to the smallest

features that can be reliably manufactured, as was in the case of planar transistors, but to denote a new generation of process technology and devices that offer better performance and efficiency than their predecessors. This technique, known as monolithic 3D integration, involves the fabrication of thinner functional tiers separated by interlayer dielectrics and interconnected via monolithic inter-tier vias<sup>12</sup>. Several predictions and analyses already highlight the opportunities and advantages of monolithic 3D integration, including increased interconnect density, reduced electrical parasitic capacitance, enhanced energy efficiency and better performance<sup>13–16</sup>. The future technologies will integrate novel 3D IC packaging and integration solutions with monolithically 3D-integrated individual chips.

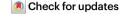

It is interesting to note that, despite its conception in the 1980s 17-19, initial research on 3D integration was not actively pursued. This lack of interest was due to the then-prevalent trend of downsizing individual silicon-based transistor dimensions – a process made feasible through advances in materials science, electronics and nanofabrication. Consequently, transistor device dimensions shrank dramatically, transitioning from the micrometre regime to the realm of tens of nanometres. This period marked the introduction of high-κ dielectrics and strained silicon technology, as well as a shift from the classical planar field-effect transistor (FET) structure to newly emerging architectures. These include non-planar fin-shaped FETs (finFETs), gate-all-around (GAA) FETs (also known as nanosheet FETs, ribbon FETs, and multi-bridge channel FETs), and the potentially forthcoming forksheet FETs and complementary-FETs<sup>20-22</sup>. This evolution, which began in 1959, is depicted in Fig. 1a. However, it is challenging to scale transistors down further by reducing the thicknesses of semiconductor channels to less than 3 nm, because of inherent issues in silicon and other bulk semiconductors, such as increased charge carrier scattering at the semiconductorinsulator interface and subsequent mobility degradation<sup>23,24</sup>. Along these lines, among other contenders such as carbon nanotubes and nanowires, ultrathin 2D semiconductors emerge as promising materials to facilitate the continued miniaturization of transistor dimensions<sup>25</sup>.

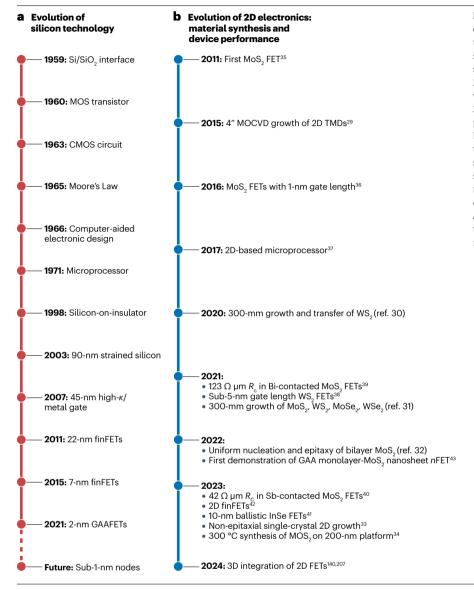

From a materials perspective, 2D semiconductors, particularly transition-metal dichalcogenides (TMDs), have drawn tremendous attention in the past decade with demonstrations of high-quality waferscale synthesis, high-performance FETs, in-sensor and in-memory computing, optical, biological and chemical sensors, scaled FETs, and so on  $^{26-28}$ . The progression in the development of growth technologies  $^{29-34}$ for 2D TMDs and the performance of their electronic devices  $^{35\text{--}43}$  is illustrated in Fig. 1b. Apart from that, 2D materials also have applications in twistronics, spintronics, straintronics, valleytronics and flexible  $electronics^{44-48}. Hence, as shown in Fig. {\color{red}2}, 3D integration with 2D electronics^{44-48}. The state of the sta$ tronics not only presents alternative pathways for scaling individual devices in line with the 'more Moore' approach (continued scaling in accordance with Moore's law) but also provides diverse functionalities that can be leveraged to co-design and incorporate non-computational devices within the same platform, facilitating the realization of 'more than Moore' technologies<sup>49</sup>. In addition, theoretical studies have predicted that incorporating 2D electronics into monolithically integrated 3D chips can increase the integration density<sup>50</sup>.

Here, we review the progress towards 3D integration of 2D electronics and its prospects and challenges. The review begins with a section on progress and challenges towards very-large-scale integration (VLSI) of 2D electronics followed by a summary of various 3D IC demonstrations that use 2D materials. Finally, we conclude this Review with a section on comprehensive device design considerations and the associated challenges.

Fig. 1 | Evolution of silicon technology and 2D electronics. a, Evolution of silicon-based transistor technology highlighting key milestones achieved since 1959. b, Evolution of 2D electronics: material synthesis and device performance. Although the first 2D material – graphene – was discovered in 2004. it was not until 2011 that the first transistor based on a 2D semiconductor was demonstrated. Since then, the performance of 2D-based field-effect transistors (FETs) has substantially improved, surpassing existing silicon technology in some instances. MOS, metal-oxidesemiconductor; CMOS, complementary metal-oxidesemiconductor; MoS<sub>2</sub>, molybdenum disulphide; MoSe<sub>2</sub>, molybdenum diselenide; MOCVD, metal-organic chemical vapour deposition; WS2, tungsten disulphide;  $R_{c}$ , contact resistance;  $\kappa$ , the dielectric constant; TMD, transition-metal dichalcogenides. Data are taken from refs. 29-43,140,207.

# Towards very-large-scale integration of 2D electronics

Here, we succinctly highlight the advances in various facets of 2D electronics, while simultaneously addressing the immediate challenges that need to be met. Overcoming these obstacles is imperative for the eventual realization of industrial-scale production of 2D-based 3D ICs.

### **Material synthesis**

Growth techniques for 2D materials have evolved considerably from mechanical exfoliation since the discovery of graphene. Initially, wafer-scale synthesis efforts included the chemical vapour deposition (CVD) of  $\mathsf{MoS}_2$  on  $\mathsf{SiO}_2$  substrates, achieving millimetre-scale coverage  $^{\mathsf{S1},\mathsf{S2}}$ . By 2015,  $\mathsf{MoS}_2$  and  $\mathsf{WS}_2$  synthesis expanded to 4-inch  $\mathsf{SiO}_2/\mathsf{Si}$  wafers using metal–organic chemical vapour deposition (MOCVD). Simultaneously, the synthesis of  $\mathsf{MoS}_2$  on other substrates, such as  $\mathsf{Al}_2\mathsf{O}_3$ ,  $\mathsf{HfO}_2$  and  $\mathsf{SiN}$ , was also reported  $^{\mathsf{29}}$ . In 2017, IMEC used atomic layer deposition (ALD) or plasma-enhanced CVD to fabricate back-end-of-line (BEOL)

compatible WS<sub>2</sub> transistors on 300-mm SiO<sub>2</sub>/Si wafers<sup>53</sup>. In 2018, ~6-inch batch production of MoS<sub>2</sub> on soda-lime glass via a face-to-face metalprecursor feeding route in a CVD process was demonstrated<sup>54</sup>. In 2021, Intel identified CVD growth from pre-patterned seeds, and MOCVD as leading techniques for synthesizing MoS<sub>2</sub>, WSe<sub>2</sub>, MoSe<sub>2</sub>, and WS<sub>2</sub> on 300-mm SiO<sub>2</sub>/Si wafers, which provides both transfer and direct deposition options<sup>31</sup>. Concurrently, epitaxial growth of 2D TMDs on sapphire substrates (via CVD or MOCVD) made strides owing to the high quality and uniformity of the synthesized 2D crystals<sup>55,56</sup>. In addition, step engineering of growth substrates and adjustable growth conditions could control the nucleation and growth direction, making it possible to obtain wafer-scale uniform single-crystal films of MoS<sub>2</sub> (refs. 57,58),  $WS_2$  (ref. 59) and  $WSe_2$  (ref. 60). Changing growth conditions can alter the nucleation of 2D materials on step edges, so that it transitions from occurring predominantly at the top edge to the bottom edge of the step, thus shifting the preferred domain orientation. A recent advance has been made in the uniform nucleation and epitaxial growth of bilayer

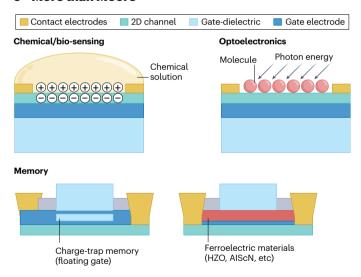

### a 3D integration of 2D electronics

#### b 'More Moore'

### c 'More than Moore'

MoS<sub>2</sub>, achieving ON-state FET performance that aligns with the International Roadmap for Devices and Systems 2028 objectives  $^{32}$ . In 2023, non-epitaxial single crystal 2D growth by geometric confinement was demonstrated  $^{33}$ . Direct growth of MoS<sub>2</sub> on 200-mm silicon complementary metal–oxide–semiconductor (CMOS) circuits at 300 °C (ref. 34), and on flexible substrates such as polymers and ultrathin glasses at 150 °C (ref. 61), aligns well with 3D integration needs because of their low thermal budgets. However, achieving epitaxial quality across all 3D stack tiers is essential for industrialization. Sequential monolithic 3D integration based on the transfer of 2D materials from growth

**Fig. 2** | **3D Integration of 2D electronics. a**, Schematic of 3D integration of 2D electronics: additional functionalities such as sensing and storage with logic can be enabled in a 3D integrated chip based on 2D materials. **b**, 'More Moore'. 2D field-effect transistors (FETs) can provide scaling benefits when introduced in gate-all-around FETs (GAAFETs) (right) and stacked FETs (also known as complementary-FETs) (left). c, 'More than Moore'. 2D FETs can also facilitate the integration of non-computational devices within 3D architectures for applications in chemical/bio sensing, optoelectronics and memory. Part **a** reproduced from ref. 207, Springer Nature Limited.

substrates to target chips or wafers could be another option. We note that the underlying substrate properties will be different for the fabrication of the second tier of devices in comparison to the first tier because the fabrication steps and conditions will have to be adjusted in order not to cause any damage to the already fabricated tier-one devices. (Here, the word tier is used to refer to different levels of device). In contrast, the general high temperature and substrate requirements for epitaxial synthesis makes the transfer process promising for 3D stacking. Regardless, controlling film thickness and uniformity, and minimizing defects and contamination during synthesis or transfer, are vital for optimizing the yield and variability of 2D FETs. Furthermore, surface treatments of the 2D channels 31,62 during tier-two fabrication might affect bottom-tier device performance, thus necessitating comprehensive studies on both the 2D-material-contact interfaces and the interlayer-dielectric-2D-material-gate-dielectric interfaces (depending on the device architecture; 2D material will not have an interface with the interlayer dielectric in a gate-all-around architecture, but can form an interface in the case of planar devices) of tier-one devices before and after fabrication of tier-two devices. Although both direct deposition and transfer approaches show potential, the ideal technique for 3D integration of 2D FETs remains to be determined.

### Transfer process in 2D electronics

Following epitaxial growth, 2D materials can be transferred from high-temperature growth substrates to desired target substrates (with pre-fabricated back-gate dielectric stack or substrates for topgate processing) using (1) polymer-assisted wet transfer methods, (2) polymer-free transfer methods or (3) deterministic dry transfer methods<sup>63</sup>. We note that the use of polymers and associated cleaning steps often induces undesirable defects in the 2D films. From an industrial perspective, the ideal technique must enable high-throughput wafer-scale 2D transfers with high yield and clean interfaces. Some of the earlier notable attempts involved transfer of 5-cm-diameter 2D-material wafers<sup>64,65</sup>. Water-based etching-free 6-inch MoS<sub>2</sub> transfer using a ethylene vinyl acetate/polyethylene terephthalate stack was demonstrated in 2018 (ref. 54). Similarly, IMEC has demonstrated 300-mm transfer of WS<sub>2</sub> using temporary wafer-to-wafer bonding and a laser debonding technique 38,66. In 2022, TSMC utilized evaporated Bi as a gentle adhesive layer to perform 2-inch WS<sub>2</sub> dry transfer<sup>67</sup>. There also exist Au-assisted 2D transfer processes, as shown previously<sup>57,68</sup>. Recently, IMEC developed the collective die-to-wafer (CoD2W) technique and demonstrated a two-step residue-free transfer of both  $MoS_2$  (epitaxial growth on 2-inch sapphire using water intercalation) and WS<sub>2</sub> (grown on SiO<sub>2</sub> with completely dry debonding) to 300-mm target wafers using adhesive-coated glass carriers<sup>69</sup>. From an automation perspective, a notable demonstration involved 100  $\mu$ m  $\times$  100  $\mu$ m 2D transfer with high speed and precise angle control using a robotic assembly<sup>70</sup>. In addition, 2D FETs suffer from the phenomenon of Fermi-level pinning<sup>71</sup>,

which causes the Schottky barrier height at the metal–semiconductor junction to be independent of the metal work function, leading to less control when engineering the contact resistance. Some studies suggest that Fermi-level pinning can be somewhat alleviated by minimizing the defects in the 2D channel during contact deposition  $^{72-74}$ . As a result, the technique of transferring pre-assembled arrays of metal contacts onto the 2D semiconductor is becoming a promising alternative for contact engineering  $^{74-78}$ . Similarly, there have been various demonstrations of dielectric transfer  $^{79-81}$ . These demonstrations, including those from industry, point towards the potential of the transfer process as a scalable integration step in 2D electronics.

To effectively execute a transfer strategy for 2D electronics, several crucial metrics must be considered. These include the ability to transfer large-area films at the wafer level while ensuring the structural integrity of the transferred films. Achieving scalability and automation is imperative for industry acceptance. Additionally, the interface of the transferred 2D material and the target substrate should not contain defects or contaminants. Uniformity and reproducibility across the entire wafer, minimizing device-to-device variation, are critical for reliable outcomes. But we note that, even though transfer techniques show promise, an ideal scenario would involve high-quality growth of 2D materials at BEOL-compatible temperatures.

### Threshold voltage engineering

Managing the threshold voltage ( $V_{TH}$ ) of a FET allows control over its ON-state. This critical parameter depends on factors such as the gate dielectric, the work function of the gate metal, and the unintentional or intrinsic doping within the 2D material. In the realm of digital circuits designed for low power consumption, minimizing the  $V_{TH}$  is paramount. With increasing chip density, there has been a corresponding rise in power consumption, resulting in undesirable levels of heat generation. In this context, maintaining a low operating voltage is crucial, which requires precise control over  $V_{TH}$  for both n-type and p-type FETs. Furthermore, CMOS circuits demonstrate optimal performance only when the  $V_{TH}$  for both n-type and p-type FETs are carefully calibrated. Suboptimal  $V_{TH}$  values can substantially affect signal propagation within CMOS circuits. Overall,  $V_{TH}$  engineering is vital to meet the specific requirements of various electronic applications. In Si-based CMOS technology, doping in the semiconductor channel and altering the work function of the gate electrode material are used for finely tuning  $V_{\text{TH}}$ . However, comparable progress in  $V_{\text{TH}}$  engineering of 2D electronics is still limited. Techniques such as substitutional doping and surface charge-transfer doping (SCTD) can be used to control the  $V_{TH}$ of a 2D FET. Substitutional doping involves the substitution of cationic and anionic elements with foreign atoms that have similar radii<sup>82</sup>. For p-type doping, cationic elements like niobium (Nb), tantalum (Ta) and vanadium (V) can be used, while rhenium (Re), hafnium (Hf), and zirconium (Zr) are utilized for n-type doping 83-87. Despite demonstrations of  $devices\,utilizing\,doped\,TMDs^{88-91}, achieving\,a\,uniform\,impurity\,density$ and precise control at large scale, while using methods compatible with state-of-the-art Si CMOS process lines, still presents a substantial challenge. The  $V_{TH}$  in p-type WSe<sub>2</sub> FETs can be modulated by adjusting the percentage of V atom doping<sup>85</sup>. This modulation was achieved by precisely controlling the partial pressure of precursors during MOCVD growth. Another challenge with substitutional doping of 2D materials arises from the fact that the ionization energy of dopants is substantially higher (by an order of magnitude) than their ionization energies in bulk semiconductors. This discrepancy is attributed to the quantum confinement effects observed in 2D materials. Consequently, dopant concentrations exceeding one atomic per cent, which far surpass the levels used in traditional doping, are necessary to alter the transport properties of 2D TMDs. Such high doping concentrations can degrade the field-effect mobility of the devices owing to an increase in scattering centres. The exact doping concentration required for mobility degradation cannot be stated because it is influenced by various factors, such as the nature of the dopant atom (atomic mass) and the characteristics of the 2D film<sup>92</sup>. Limited research has been conducted into the impact of doping concentration on mobility degradation, making it a prospective area for future investigation. This issue could be mitigated if the dopant were to create shallower donor levels, allowing for easier carrier activation. In this regard, Re is a transition metal known to form shallow donor levels with MoS<sub>2</sub> (refs. 93,94). MoS<sub>2</sub> monolayers can be n-doped by substituting Mo with Re atoms, achieving controllable concentrations down to 500 parts per million using MOCVD<sup>87</sup>. Their findings demonstrated that an increase in Re concentration led to a reduction in the number of sulfur (S) vacancies, resulting in a shift in  $V_{\rm TH}$  and subsequently enhanced device performance. The higher free energy of formation of S vacancies as a result of Re doping has been claimed to be the reason for fewer S vacancies. This substitutional approach can also be extended to anionic replacement 95-97.

Another doping approach for modulating  $V_{TH}$  of devices is SCTD. For the effective implementation of the SCTD approach, it is essential to meticulously design the gate stack. This design should ensure three key aspects: (1) the equivalent oxide thickness (EOT) must remain unaffected, (2) the gate control should be maintained, and (3) the channel material must not suffer any damage. In SCTD, dopant atoms are attached to the 2D material through either a chemical bond or a physical interaction, resulting in a charge-transfer process. The direction of charge transfer is determined by the Fermi-level difference between the dopant and the host materials, dictating whether the adsorbed dopant functions as an acceptor or a donor. Unlike substitutional doping, SCTD does not introduce any lattice disorders, because dopants are positioned outside the electrical carrier pathways. As a result, SCTD in general enables the retention of higher electrical mobility in the 2D materials. SCTD has been successfully demonstrated in various TMDs, allowing for both *n*- and *p*-type doping with different degrees of effectiveness 98,99.

Additionally, ozone or oxygen plasma treatment can be applied to transform the top layer of TMDs into their corresponding substoichiometric oxides, resulting in substantial p-type doping in the layers below<sup>100</sup>. The previous study shows that converting atomically thin WSe<sub>2</sub> to WO<sub>x</sub> led to strong hole-doping owing to electron transfer from the underlying WSe<sub>2</sub> to the surface WO<sub>x</sub> (ref. 101). Doping can also be induced by depositing a sub-stoichiometric insulator on top of the 2D material. This doping can occur through two processes. The first involves the transfer of charge due to trap states at the semiconductor/oxide interface or in the oxide near the interface (such as border traps). The second process involves doping the 2D material via the transfer of electrons or holes from states that do not overlap with the energy gap of the 2D semiconductor. The challenge lies in achieving doping through this latter process, given that it does not degrade the subthreshold slope and mobility of the device. It has been demonstrated that an improvement in the device performance can be achieved, along with a large  $V_{\rm TH}$  shift of around 20 V, by depositing aluminium oxide<sup>102</sup>. Other oxides, like amorphous titanium suboxide<sup>103</sup>, molybdenum trioxide<sup>100,101,104</sup> and silicon nitride<sup>105</sup> have also exhibited similar behaviour. These avenues hold promise for addressing the  $V_{\text{TH}}$  engineering challenges in both n- and p-type 2D FETs, a crucial

step towards realizing 2D CMOS circuits. Studies have also explored tuning the threshold voltage by incorporating an interfacial layer in the gate dielectric, with a predominant focus on silicon. As a result, a shift in flat band voltage can be obtained by introducing titanium (Ti) and Hf in a metal/high- $\kappa$  gate stack<sup>106</sup>. Even though there is a scarcity of research on 2D materials concerning the dipoles originating from the gate dielectric, research into dipoles induced by organic polymers, capable of altering the threshold voltage in 2D materials, has been conducted 92,107,108. In another study, gadolinium aluminate was used in the dielectric stack to gain control over the threshold voltage 109.

In addition to all this, it is also important to note that device-to-device variation can stem from defects in the as-grown 2D material or at the interface between the 2D material and the dielectric. Acceptable device-to-device variability is thus a crucial milestone for 2D electronics which is yet to be achieved  $^{110}$ . Thus, threshold voltage engineering techniques must be developed hand-in-hand with interface engineering and a focus towards reducing device-to-device variation on the large scale.

### Yield, variability and dielectric integration

In addition to  $V_{\rm TH}$  engineering, achieving high device yield and minimizing device-to-device variability are other crucial prerequisites when designing and demonstrating large-scale CMOS circuits. While device yield affects the effective design of integrated circuits, such as the footprint, uniformity in device performance is essential for the proper operation of CMOS circuits (achieving correct voltage levels).

Transferring synthesized 2D materials poses challenges owing to their atomically thin and exceedingly delicate structure. Moreover, the capillary forces that arise when the film is removed from the solution bath can cause the material to wrinkle, fold and crack. Conversely, direct growth of 2D materials on substrates suitable for commercial applications is often constrained by the requirement for high growth temperatures, the use of chemically reactive precursors and the need for epitaxial alignment. Such elevated growth temperatures can cause the deterioration of the underlying substrate, thereby adversely affecting device performance and reliability [111-113].

To improve the yield and reliability of 2D FETs, in addition to finetuning or eliminating the transfer process, there is a need for comprehensive optimization in both the growth of 2D materials and process integration. The growth of 2D materials must be a very precise and controlled process in order to control the quantity of vacancies and defects, with the ultimate goal of ensuring that the as-grown material exhibits minimal vacancies and defects. A uniform crystalline film is also essential to achieve good yield and better reliability. The number and distribution of grain boundaries can play a part in determining both the performance and uniformity of devices. Devices that are smaller than the average grain size tend to be less affected by these boundaries, whereas larger devices are more susceptible to their influence. In particular, a device located directly on a grain boundary can experience pronounced effects. The variability in device characteristics, especially when comparing devices with different numbers of grain boundaries, is an important consideration. However, this variability can be mitigated by increasing the grain size and improving the growth process, thereby making the material more uniform. While addressing the challenges posed by grain boundaries is an ongoing area of research, it is worth noting that they might not necessarily be a limiting factor in device variation. This is especially true given the sizes of domain typically achieved in current 2D-material growth techniques. Additionally, on a circuit level, the tolerance for device-level variability tends to be higher. Circuits can often accommodate a certain degree of variation in individual components without notable loss of overall functionality. This inherent resilience could mean that grain boundaries, although a critical factor in device variation, might not be a critical obstacle. Therefore, although grain boundaries can contribute to device variability, their eefect might be less critical at the circuit level. Continued research and development in material growth and processing techniques will further clarify their role and potential ways to mitigate their effects on device performance. Therefore, grain boundaries are a crucial factor to consider, but they do not inherently preclude the effective use of 2D materials in scaled devices.

Additionally, mitigating device variability involves fine-tuning contact formation, optimizing the integration of gate dielectrics and incorporating effective post-fabrication device treatments or annealing steps. In this context, it is worth noting a study 110 in which the effect of imperfections of individual FETs on 2D-based electronic circuits was thoroughly examined. The authors emphasize the importance of electrically active traps that can arise from defects at various points in the FET structure, such as the channel, the dielectric and the interface between the channel and the dielectric. These traps can introduce variability in  $V_{TH}$  of individual devices, underscoring the need for meticulous optimization. Thus, the advances towards the development of high-density 3D CMOS circuits built upon 2D FETs must also prioritize enhancing yield through the optimization of synthesis, transfer and fabrication processes. Equally crucial is the selection of a compatible 2D-material-dielectric combination that minimizes device-to-device variability. Even though device variability was not studied, there has recently been some work on incorporating crystalline dielectrics such as CaF<sub>2</sub> (ref. 114) and SrTiO<sub>3</sub> (ref. 79) with low EOT in 2D electronics.

In addition, the integration of ultrathin high- $\kappa$  dielectrics with 2D materials is a crucial component, particularly in GAA device architectures. To achieve successful integration of scaled dielectrics, two critical factors are essential: low leakage currents (less than 10<sup>-2</sup> A cm<sup>-2</sup>) and high dielectric strength (greater than 10 MV cm  $^{-1}$ )  $^{115,116}$ . The attainant ment of these characteristics is closely tied to having a high dielectric constant and a large bandgap. Noteworthy materials that meet these specifications include HfO<sub>2</sub>, with a dielectric constant of approximately 23, and CaF<sub>2</sub>, with a bandgap of around 12 eV. It is important to highlight that within this context, the physical thickness of the dielectric layer is not as vital as the EOT. The primary objective is to minimize the EOT to less than 1 nm. Substantial strides have been made towards this objective, such as the achievement of reducing HfO<sub>2</sub> thickness to attain an EOT of less than 1 nm, alongside an impressive ON-state current  $(I_{ON})$  performance of approximately 420  $\mu$ A  $\mu$ m<sup>-1</sup> in a dual-gated MoS<sub>2</sub> MOSFET configuration. This approach incorporated an interfacial layer of gadolinium aluminate within the dielectric stack, thereby enabling effective  $V_{TH}$  control and enhancing carrier transport properties<sup>109</sup>. Additionally, the capability to achieve an EOT of 1 nm for graphene, MoS<sub>2</sub>, and WSe<sub>2</sub> devices has been demonstrated, attributed to the use of an ultrathin (~0.3 nm) layer of perylene-tetracarboxylic dianhydride (PTCDA) molecular crystals as a seeding layer. CaF2 insulators could also enable scaling down to less than 1 nm EOT (with a physical thickness of 2 nm), thereby achieving not only low leakage currents but also competitive device performance, including a subthreshold swing down to 90 mV dec<sup>-1</sup> (ref. 117). These advances underscore the importance of novel approaches in the pursuit of scaled dielectrics with enhanced electrical properties. Apart from that, GAA deposition techniques for 2D materials have been demonstrated, but further exploration into integration challenges such as the damage to the 2D

channels during gate-stack or contact formation is necessary  $^{118}$ . GAA single-layer MoS $_2$  devices, for instance, have shown an  $I_{\rm ON}$  of 410  $\mu\rm A~\mu m^{-1}$  and a subthreshold swing of 220 mV dec $^{-1}$ , indicating the viability of GAA architectures for 2D materials  $^{43}$ . However, the variety of dielectric stacks and gate metals used in various studies makes direct comparison of the findings challenging. Therefore, a new parameter, the projected threshold voltage variation ( $S\sigma V_{\rm TH}$ ), has been introduced to facilitate comparisons across various studies on 2D materials and with the silicon industry  $^{119}$ . As a result, a relatively low  $S\sigma V_{\rm TH}$  value of 33 mV was obtained, compared with those of state-of-the-art ultra-thin-body silicon-on-insulator and silicon fin FETs, which were 13 and 20 mV, respectively  $^{120,121}$ . Addressing the concerns discussed in this section is pivotal for further improvements in reducing threshold voltage variation.

### **Device performance**

Despite various advances, the performance of 2D FETs is still hindered by contact limitations. The primary issue revolves around achieving contacts that demonstrate ohmic behaviour. In contrast to silicon-based devices, where low-resistance ohmic contacts are obtained through precise doping via ion implantation of the underlying silicon beneath the metal, replicating such results in 2D materials is hindered by their atomically thin nature. Additionally, the process of engineering contacts for 2D materials is further complicated by phenomena such as Fermi level pinning<sup>71</sup>. Ongoing research in the field of 2D materials has recently led to breakthroughs demonstrating ultralow contact resistance in these materials, surpassing the capabilities of traditional silicon-based CMOS technologies and meeting the targets set for 2028 by the International Roadmap for Devices and Systems. A notable achievement includes the realization of ultralow contact resistance of 123 Ω μm using bismuth (Bi) contacts<sup>39</sup>. However, it is not practical to use Bi owing to its low melting point (below 300 °C), prompting a shift towards antimony (Sb) as a more viable contact metal for MoS<sub>2</sub> thanks to its higher melting point (above 600 °C). This switch has enabled the demonstration of ultralow contact resistance of  $42 \Omega \mu m$  (ref. 40) and reported currents exceeding 1 mA μm<sup>-1</sup>. Further progress has been seen in achieving the on-state current  $(I_{ON})$  of 1.27 mA  $\mu$ m<sup>-1</sup> (at a drain-to-source voltage of 2.5 V) in short-channel (50 nm) FETs based on bilayer MoS<sub>2</sub>.

In another report, the FETs made from mechanically exfoliated InSe flakes showed ballistic transport achieved by using a phase-transition method induced by yttrium doping  $^{122}$ . The channel length could be scaled down to 10 nm while attaining a contact resistance as low as 62  $\Omega$  µm. Although these results hold promise, further exploration is required for reproducibly achieving such high performance on a larger scale. Furthermore, the successful integration of large-scale 2D CMOS requires comparable performance from both n-FETs and p-FETs. While substantial progress has been made in achieving high ON currents for n-type 2D FETs, replicating these successes for p-type counterparts has presented remarkable challenges as given below.

### p-type 2D FETs

Two major obstacles towards p-type 2D FETs include Fermi-level pinning and substrate-induced electron doping by charge transfer<sup>123</sup>. The Fermi-level pinning is generally believed to be caused by (1) defects in the metal–semiconductor interface (which could be intrinsic defects in the 2D semiconductor, defects generated with the deposition process, adsorbates or other contaminants), (2) strain at the metal–semiconductor interface causing bandgap changes, or (3) reduction of the metal work function due to the formation of interface dipoles caused by the electron density redistribution at the

metal-semiconductor junction. In addition to Fermi-level pinning, substrate induced charge transfer electron doping of 2D semiconductors is also observed, which can be caused by impurities or atomic vacancies in the dielectrics<sup>123</sup>. In most cases, the above-mentioned effects are unfavourable for achieving hole transport and thus, 'purely' p-type 2D FETs (without any *n*-branch). However, some recently published research aimed to achieve p-type 2D FETs with either substitutional doping (mentioned in the section 'Threshold voltage engineering') or contact engineering strategies. In terms of contact engineering, transferring high-work-function metals in van der Waals metal-semiconductor junctions has helped to achieve better hole transport 74,76,78. Inserting a buffer material such as In or Se between the semiconductor and contact metal was also used to achieve clean and less-damaged contacts<sup>73,124</sup>. Another route, distinct from the above-mentioned techniques, is the treatment of WSe<sub>2</sub> after growth to achieve hole transport. For example, oxygen plasma treatment on transferred WSe<sub>2</sub> flakes<sup>125</sup>, immersion of WSe<sub>2</sub> in an aqueous solution of 4-nitrobenzenediazonium tetrafluoroborate (4-NBD)<sup>126</sup> and exposing WSe<sub>2</sub> devices to nitric oxide gas flow<sup>62</sup>, have all helped to achieve p-type 2D FETs. In another distinct approach, VSe<sub>2</sub> was grown on WSe<sub>2</sub>, followed by the formation of cracks to achieve small channel p-type FETs with atomically clean interfaces 127. Recently, another demonstration involved p-type electrical contacts for 2D TMDs such as (exfoliated) WSe<sub>2</sub> fabricated with industry-compatible electron-beam evaporation of high-work-function metals such as Pd and Pt<sup>72</sup>. Though promising, more such efforts are required in order to improve p-FETs and reach the performance levels of 2D n-FETs. Only then, can we achieve 2D CMOS, which can evolve to VLSI of 3D CMOS with 2D electronics.

The above discussion has provided insights into advances in 2D semiconductor research, encompassing contributions from both academic and corporate research environments. Leading semiconductor giants such as Intel and TSMC have notably incorporated 2D materials into their roadmaps. Corporate research initiatives in the field of 2D semiconductors are outlined in Box 1, offering an overview of some of their key findings and accomplishments to date (including some reports that have been discussed above). Recently, Intel also published an article on their perspective on 2D transistors including discussions on challenges and strategies associated with deposition of 2D materials, formation of stacked 2D nanoribbon channels, doping, gate-dielectric/contact formation and contact resistance <sup>118</sup>.

Researchers in the 2D electronics field must establish realistic objectives. For silicon-based technologies, these targets are typically provided by the International Roadmap for Devices and Systems. In the realm of 2D electronics, a comprehensive set of targets has been identified, outlining intermediate, critical and long-term goals for 2D transistors. These targets are crucial for the transition from laboratory to real-world applications <sup>128</sup>. Specifically, the critical targets for high-performance  $I_{\text{ON}}$ , low-performance  $I_{\text{ON}}$ , mobility ( $\mu$ ), external resistance and subthreshold swing are 1.5 mA  $\mu$ m<sup>-1</sup>, 1 mA  $\mu$ m<sup>-1</sup>, 500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 200  $\Omega$   $\mu$ m and 65 mV dec<sup>-1</sup>, respectively. These parameters are essential for achieving VLSI of 2D electronics.

### 3D integration of 2D electronics

3D integration of 2D materials has various applications, as depicted in Fig. 3. These applications can fall into two categories: (1) stacking 2D materials to maximize area utilization and facilitate scaling, and (2) integrating 2D materials or devices on top of silicon-based logic or memory devices. The following sections provide a summary of these topics.

### Box 1

## Corporate research on 2D transistors

Although it is thought that applying 3D integration to current silicon technology could extend scaling to the end of this decade, the inherent limitations of a bulk semiconductor like silicon will eventually require the integration of sub-3-nm semiconducting channels. Consequently, owing to the theoretical promise of transistor size scaling — that the number of semiconducting channels can be increased by using a 2D material instead of a bulk semiconductor<sup>208</sup> — as well as the substantial research into 2D transition-metal dichalcogenides by academic institutions, semiconductor companies such as Intel, TSMC and IMEC have started to develop transistors based on 2D semiconducting channels, as shown in the table below. Since 2019, corporate research into 2D transition-metal dichalcogenides has accelerated. Examples of the key findings and accomplishments are summarized in the table.

In addition to corporate research on 2D TMDs, various industries are focusing on developing tools and equipment to produce 2D materials. For example, MOCVD manufacturing companies such as Aixtron and Veeco are playing a substantial part in the growth of 2D materials. Moreover, emerging companies like 2D Factory demonstrate potential for scaling 2D material production to the industrial scale. Although graphene is a semi-metal, it shows promise in applications such as electrostatic interference barriers. In this context, Graphenea has emerged as a prominent player in the graphene-manufacturing industry. We believe these industries will make remarkable progress in tool development and the growth of 2D materials, enabling the widespread adoption of 2D electronics.

| TSMC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019  | Made the first top-gated $WS_2p$ -FET on a $SiO_x/Si$ substrate by using channel area-selective chemical vapour deposition (CVD) growth <sup>209</sup> .                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2020  | Obtained a record high ON-state current ( $V_{ON}$ ) of 390 $\mu$ A $\mu$ m <sup>-1</sup> for CVD-grown monolayer MoS <sub>2</sub> $n$ -FET. The contact resistance ( $R_{C}$ ) was decreased to ~1.1 k $\Omega$ $\mu$ m for a channel length of 100 nm, and the thickness of the HfO <sub>x</sub> gate was scaled down to 10 nm (an equivalent oxide thickness of 2 nm) <sup>210</sup> .                                                                                                                                                                      |

| 2021  | Demonstrated an ohmic contact with a near-zero Schottky barrier height and achieved a contact resistance value of $660\Omega\mu m$ with Sb contacts. This advance led to the realization of an $I_{ON}$ of 1,000 $\mu$ A $\mu$ m <sup>-1</sup> at a $V_{DS}$ of 2V. Importantly, these transistors demonstrated robustness under high-temperature treatments (over 300 °C), making them compatible with back-end-of-line (BEOL) processes. The transistors maintain a high $I_{ON}$ of ~375 $\mu$ A $\mu$ m <sup>-1</sup> at a drain voltage of 1V (ref. 211). |

| 2022  | Introduced a technology computer-aided design model that enabled the precise extraction of different device parameters from experimental data of metal-oxide-semiconductor field-effect transistors (MOSFETs) with 2D channel backgated <sup>212</sup> . Drain-current versus back-gate voltage ( $I_D$ - $V_{BG}$ ) data of transistors with channel lengths ranging from 0.5 $\mu$ m to 5 $\mu$ m were used as the experimental data for the model.                                                                                                          |

|       | Reduced the contact resistance of WSe <sub>2</sub> by about 100 times to around $1k\Omega\mu m$ by charge transfer from layered oxide materials to WSe <sub>2</sub> (ref. 213). Realized both $n$ - and $p$ -FETs by using WSe <sub>2</sub> . By using Sb or Pt contacts and through the integration of advanced oxide-based encapsulation and doping techniques, a low $R_0$ of $750\Omega\mu m$ and $1.8k\Omega\mu m$ were achieved for the $p$ -FET and $n$ -FET, respectively <sup>214</sup> .                                                             |

| 2023  | Demonstrated an impressive $R_{\rm c}$ value of below 100 $\Omega$ µm with reduced contact lengths. Sb-contacted monolayer MoS <sub>2</sub> transistors demonstrated a $R_{\rm c}$ value of 164 $\Omega$ µm for a contact length of 30 nm at a carrier concentration of 1.4×10 <sup>13</sup> cm <sup>-2</sup> (ref. 215).                                                                                                                                                                                                                                      |

| Intel |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2021  | By using CVD and MBE, $MoS_2 n$ -FETs and $WSe_2 p$ -FETs were obtained with a contact resistance of around $400 \Omega \mu m$ for $n$ -FETs <sup>216</sup> .                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Demonstrated the first-time growth of MoS <sub>2</sub> , WSe <sub>2</sub> , WSe <sub>2</sub> and MoSe <sub>2</sub> films using metal-organic chemical vapour deposition (MOCVD) on a 300-mm wafer at BEOL temperatures <sup>31</sup> .                                                                                                                                                                                                                                                                                                                         |

|       | By using Sb and Ru as contacts, the performance of both $n$ -FETs and $p$ -FETs were enhanced and a record low $R_c$ of $2.7 \text{k}\Omega\mu\text{m}$ was achieved for $p$ -FETs <sup>31</sup> .                                                                                                                                                                                                                                                                                                                                                             |

| 2022  | Demonstrated devices with a channel length of 25 nm, nearly negligible drain-induced barrier lowering, and a subthreshold swing of 75 mV dec <sup>-1</sup> .  Additionally, modelling results suggested that a double-gated device could scale down to at least 10 nm with low leakage <sup>208</sup> .                                                                                                                                                                                                                                                        |

|       | Reported the growth of 2D materials on 300-mm substrates at BEOL-compatible temperatures. Additionally, an $I_{ON}$ of 100 $\mu$ A $\mu$ m <sup>-1</sup> was obtained in WSe <sub>2</sub> $p$ -FETs (grown at front-end-of-line temperatures) <sup>217</sup> .                                                                                                                                                                                                                                                                                                 |

| 2023  | 2D BEOL barriers with the thickness of 10 Å were used as interconnect barriers and reported promising barrier performance on par with their 25 Å tantalum barrier <sup>218</sup> .                                                                                                                                                                                                                                                                                                                                                                             |

| IMEC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2020  | Double-gated $WS_2$ transistors featuring a gate length as small as 18 nm were produced within a 300-mm Si complementary metal-oxide-semiconductor (CMOS) fabrication facility <sup>38</sup> .                                                                                                                                                                                                                                                                                                                                                                 |

| 2021  | Approximately 90% yield of $WS_2$ transistors were achieved on 300-mm substrates <sup>219</sup> .<br>The top-gate lengths of $WS_2$ FETs were scaled down to below 5 nm (ref. 220).                                                                                                                                                                                                                                                                                                                                                                            |

| 2023  | The collective die-to-wafer technique was developed to transfer epitaxial single-layer $MX_2$ ( $M=Mo$ , $W$ ; $X=S$ , Se) films from sapphire to 300-mm target wafers <sup>221</sup> .                                                                                                                                                                                                                                                                                                                                                                        |

#### Stacked 2D FETs

The first demonstration of 3D integrated electronics utilizing stacked 2D materials was reported in 2012 (ref. 129). This work involved the mechanically exfoliated n-type MoS<sub>2</sub> on top of a p-type Bi<sub>2</sub>Sr<sub>2</sub>Co<sub>2</sub>O<sub>8</sub> – a

layered transition-metal oxide that can be exfoliated – to create a 3D inverter. The full stack consisted of graphene (for the supply voltage node),  $Bi_2Sr_2Co_2O_8$  (p-channel), graphene again (for the output node),  $MoS_2$  (n-channel) and Ti/Au (the ground) layered on a  $Si/SiN_x$

#### a 2D on silicon logic for optoelectronics

#### **b** Monolithic 3D CMOS with 2D FETs

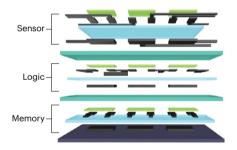

### C All-2D-based sense, logic memory

### d 2D-based Multi-bridge channel FET

### e 2D-based complementary-FETs

### f 2D with memory devices

### g Direct growth of 2D materials on silicon CMOS wafers

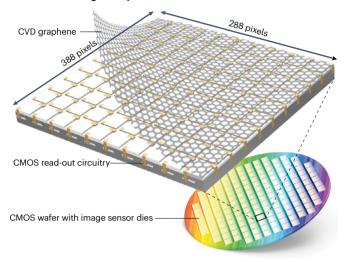

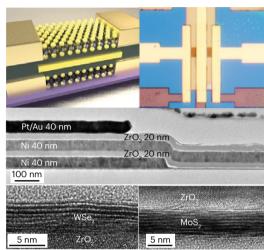

$\label{eq:Fig.3} \begin{tabular}{ll} Fig. 3 & Applications of 3D integration of 2D electronics. a, Integration of 2D materials with silicon logic for optoelectronics. b, Monolithic 3D complementary metal-oxide-semiconductor (CMOS) with 2D field-effect transistors (FETs). c, Incorporation of sensing and memory functionalities with logic, all based on 2D materials. d, 2D-based multi-bridge channel FETs. e, 2D-based complementary-FETs. f, Integration of 2D materials and memory devices. C1 and C2 denote $$MoS_2$-based transistors in first and second levels of 1-transistor/1-resistor memory cells, respectively, and C3 is used to denote the h-BN-based resistive $$$$$

random-access memory (RRAM) in the second level. **g**, Direct growth of 2D materials on silicon CMOS wafers for 2D-silicon heterogeneous 3D integration. h-BN, hexagonal boron nitride; BEOL, back-end-of-line; MOCVD, metal-organic chemical vapour deposition; ZrO<sub>2</sub>, zirconium dioxide. Part **a** reproduced from ref. 142, Springer Nature Limited. Part **b** reproduced from refs. 130,131, Wiley. Part **c** reproduced from ref. 133, Wiley. Part **d** adapted with permission from ref. 136, Wiley. Part **e** reproduced from ref. 138, Wiley. Part **f** reproduced from ref. 143, IEEE. Part **g** reproduced from ref. 34, Springer Nature Limited.

substrate<sup>129</sup>. By 2015, advances had been made in the sequential fabrication of  $MoS_2$  FETs, starting with the growth of the first  $MoS_2$  layer on a  $SiO_2$ /Si wafer. This process included device fabrication at the first tier, followed by  $SiO_2$  encapsulation, and was repeated for a second-tier device. However, these devices shared a common global back-gate, and the focus was largely on the MOCVD growth of 2D materials on 4-inch  $SiO_2$ /Si wafers, rather than on 3D integration<sup>29</sup>.

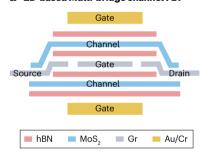

Substantial progress in 3D integration was reported in 2016 (ref. 130) (Fig. 3b), showcasing the use of mechanically exfoliated 3–7-nm-thick  $MoS_2$  and  $WSe_2$  flakes as n- and p-type channel materials, respectively, with 20-nm-thick  $ZrO_2$  deposited via atomic layer deposition as the gate dielectric. The corresponding NMOS and PMOS devices had gate length/width dimensions of 2  $\mu$ m/3.3  $\mu$ m and 2  $\mu$ m/5.5  $\mu$ m, respectively. This work resulted in the fabrication of digital (inverter, NAND and NOR) and analog (amplifiers and signal mixers) CMOS circuits, marking a notable achievement in the field. Concurrently, the silicon industry's exploration of nanosheet technology for GAAFETs paralleled proposals for 3D stacking of 2D FETs, aimed at increasing drive currents (535  $\mu$ A  $\mu$ m<sup>-1</sup> ON-state currents for a channel length of 370 nm at a  $V_{DS}$  of 4.5 V)<sup>131</sup>. With a channel length/width of around 370 nm/2  $\mu$ m, they were able to increase the drive current by an order of two with the dual-channel FETs.

In 2019, evaporated 8-nm-thick Te thin films were used to fabricate and stack p-type FETs to achieve a PMOS logic 3D inverter  $^{132}$ . In addition, device statistics from around 60 individual p-type FETs were also obtained. This period also saw 2D materials being used to integrate sensing or memory functions into 3D ICs. A layer-by-layer stacking approach enabled the demonstration of devices across three tiers (Fig. 3c), utilizing exfoliated few-layer graphene and 45–47-nm-thick hexagonal boron nitride (h-BN) for gate/contact electrodes and dielectrics, respectively, with transferred CVD-grown  $\rm MoS_2$  serving as the semiconducting channel  $^{133}$ . Consequently, the first, second and third tiers comprised three two-terminal memories, three in-plane inverters and NAND gates, and three individual optical sensing FETs, respectively.

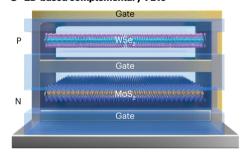

Despite these advances, challenges such as the reliance on mechanical exfoliation and the use of h-BN as the gate dielectric were limiting factors for scaling<sup>134</sup>. Nonetheless, the connection of three vertically stacked FETs demonstrated an increase in current densities ( $I_{ON} = 54 \,\mu\text{A} \,\mu\text{m}^{-1}$  at  $V_{DS} = 1 \,\text{V}$  for a 3- $\mu$ m channel length), because this design increases the effective width while maintaining the same active device area of a single FET. Further progress in 2021 included the monolithic fabrication of 3D inverters using vertically stacked n-type MoS<sub>2</sub> and p-type WSe<sub>2</sub> FETs, alongside the use of chemical doping for threshold voltage engineering 135. Exploration continued with the development of MoS<sub>2</sub>-based multi-bridge channel FETs<sup>136</sup> (Fig. 3d) and further demonstrations of 3D-integrated inverter, NAND and NOR circuits using CVD-grown MoS<sub>2</sub> and MoTe<sub>2</sub> for n-FETs and *p*-FETs, respectively<sup>137</sup>. In these devices, HfO<sub>2</sub> was used as the gate dielectric and the channel length was relatively large at 10-20 μm. The same year, another demonstration involved the fabrication of 22 complementary-FET devices with p-type WSe<sub>2</sub> FETs stacked on top of *n*-type MoS<sub>2</sub> FETs<sup>138</sup> (Fig. 3e). CVD was used to grow both 2D materials while  $HfO_2$  deposited by atomic layer deposition was used as the gate dielectric. The channel length and width were both 5 µm. A similar demonstration involved the fabrication of 3D inverters using p-type  $MoTe_2$  and n-type  $MoS_2$  (ref. 139).

The most recent notable advance in 3D-integrated 2D electronics involves the demonstration of (1) wafer-scale and monolithic two-tier 3D integration based on  $MoS_2$  with more than 10,000 FETs in

each tier; (2) three-tier 3D integration based on both MoS<sub>2</sub> and WSe<sub>2</sub> with about 500 FETs in each tier; and (3) two-tier 3D integration based on 200 scaled MoS<sub>2</sub> FETs (channel length 45 nm) in each tier<sup>140</sup>.

#### Integrating 2D with logic or memory

2D materials are being explored not only for their potential in scaling FETs but also for incorporation into BEOL transistors and applications. Early developments along this route involved the use of 2D materials for optoelectronic applications. In 2016, researchers successfully transferred CVD-grown  $MoS_2$  onto interlayer-dielectric-encapsulated silicon-based logic or memory tiers on a silicon wafer  $^{141}$ . The top tier consisted of a  $5\times 5$  phototransistor array, based on CVD-grown  $MoS_2$ , while the bottom tier comprised 6-transistor static random-access memory (6T SRAMs) using poly-silicon nanowire FETs. A transparent conducting oxide served as the top-gate metal, facilitating the light–matter interaction in 2D materials. This work also introduced the idea of using other 2D TMDs with different bandgaps for wavelength-dependent optical sensing.

The substantial potential for monolithic 3D integration of 2D materials with silicon CMOS technology was further demonstrated in 2017 with the development of a 388 × 288-pixel broadband image sensor <sup>142</sup> (Fig. 3a). This sensor was manufactured by transferring CVD-grown graphene onto a pre-fabricated silicon CMOS die, complete with vertical interconnects and read-out circuitry. Lead sulfide colloidal quantum dots were deposited onto the patterned graphene pixels, serving as the light absorption layer. The photodetection mechanism in the device arises from the photogating effect and charge transfer from the quantum dots to the graphene layer, which enables ultrahigh gain and photoresponsivity. The incorporation of graphene remarkably improved the dynamic range, responsivity and broadband detection capabilities (300–2,000 nm), showcasing the benefits of monolithic 3D integration with 2D materials.

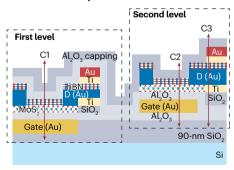

Monolithic integration has also been applied to embed memory functionalities into 2D FETs. In 2018, a team demonstrated a two-level stacked 2  $\times$  2 one-transistor, one-resistor (1T1R) array combining local back-gated MoS $_2$  transistors with h-BN-based resistive random-access memory (RRAM) devices  $^{143}$  (Fig. 3f). Despite the need for additional planarization steps owing to surface roughness, the fabrication flow emphasized the feasibility of integrating memory devices with 2D FETs in a 3D architecture.

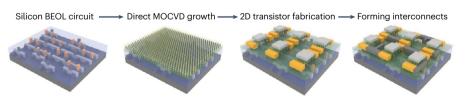

In 2022, another team transferred CVD-grown MoS<sub>2</sub> onto HfO<sub>2</sub>encapsulated p-type silicon FETs showcasing 3D inverter and two-input NAND and NOR circuits<sup>144</sup>. The channel lengths and widths of both n-FETs and p-FETs were 10 μm and 16 μm, respectively. A similar effort led to the monolithic integration of a 3D CMOS inverter, achieved by fabricating top-gated 2D FETs based on CVD-grown MoS<sub>2</sub> on top of silicon finFETs<sup>145</sup>. These advancements highlight ongoing improvements in the transfer process and the development of low-temperature waferscale growth techniques for 2D materials. A notable example includes the use of a MOCVD reactor that separates the low-temperature growth region (where the target substrate is placed) from the high-temperature chalcogenide-precursor-decomposition region. This setup enabled the direct growth of MoS<sub>2</sub> on a 200-mm silicon CMOS wafer at temperatures below 300 °C, meeting BEOL temperature requirements and facilitating the heterogeneous integration of a MoS<sub>2</sub>-silicon SRAM cell) $^{34}$  (Fig. 3g).

Similarly, 2D h-BN (-6 nm) was transferred onto pre-fabricated silicon–CMOS microchipto integrate memristors with silicon CMOS transistors, paving the way for in-memory computing with one-transistor,

one-memristor (1T1M) cells<sup>146</sup>. Beyond electronic applications, 2D materials are also being widely explored for their potential in photonic applications within a 3D-integrated architecture<sup>147</sup>. The most recent notable advance includes the demonstration of an Al-processing hardware using six layers of transistor and memristor arrays based on  $MoS_2$ ,  $WSe_2$  and  $h\text{-BN}^{140}$ . These authors utilized the capability to peel off a flexible substrate from a rigid carrier substrate after device fabrication and stack it on the target substrate. The work is an important milestone in the path towards enabling next-generation wearable electronics.

### Design considerations and challenges

Once reliable 2D-based circuits can be reproducibly manufactured on the large scale, the subsequent objective is to expand this technology into 3D integration, which presents unique challenges that demand dedicated research efforts to address. In this section, we provide a comprehensive evaluation of various design considerations that are critical for the development of 2D-based monolithic 3D ICs. We note that design considerations for electronic devices vary substantially, depending on the desired functionalities the final product is intended to perform. When it comes to heterogeneous monolithic 3D integration – combining different materials, devices and functionalities within a single chip leads to an increase in complexity. Hence, crafting chips for specific tasks requires dedicated designs and specialized process flows. The overarching goals are to improve performance, power efficiency and integration density, to minimize size and costs, to optimize resource allocation and to increase signal speed. We start by examining design considerations related to materials, devices and fabrication techniques, then move to surface planarization, thermal management and reducing electrostatic coupling, and finally conclude with a discussion of the general architectural design principles for 3D ICs.

#### Materials, devices and fabrication techniques

The selection of devices and functional blocks for a 3D chip is determined by the desired functionalities, which include n- and p-type 2D FETs, memory devices and sensors for optical, biological and chemical applications, as well as Si-based circuits, among others. Each type of device has its own set of fabrication needs and limitations, which affect the choice of materials and technologies used for creating connections between layers (inter-tier vias), insulating layers between tiers (inter-tier dielectrics), thermal dissipation and electrical interference screening layers. In addition, choosing materials for these different functionalities also requires consideration of their thermal properties, such as the coefficient of thermal expansion and thermal conductivity, as well as their compatibility with the fabrication process.

After the selection of materials for the desired devices, it is crucial to address the fabrication complexities associated with their integration into a 3D chip. For instance, in a Si-based 3D prototype, low-temperature molecular bonding of silicon-on-insulator was used to minimize performance degradation in the bottom tiers<sup>148</sup>. It is essential to evaluate the effect of process variations during the sequential fabrication of top tiers on the performance of bottom-tier devices, particularly in heterogeneous 3D integration. Key issues to consider include the presence of voids at interfaces<sup>149</sup>, the quality of inter-tier dielectrics, the occurrence of resistive shorts or opens in circuit connections and vias<sup>150</sup> and electrostatic coupling, as well as impurities and particle contamination introduced during fabrication. Each of these factors can substantially affect the overall performance of the chip across its different tiers.

### **Surface planarization**

2D semiconductors are promising for scaled FETs with sub-1-nm channel thickness. However, the reliability of these scaled FETs faces challenges due to defects caused by surface roughness and irregularities at the interfaces between 2D materials and dielectrics<sup>151</sup>. Moreover, transferring 2D materials onto non-planarized surfaces can introduce strain, negatively affecting device performance<sup>152</sup>. Additionally, the non-uniformity of growth substrates can lead to variability in device performance among different 2D FETs<sup>153</sup>, a problem that intensifies when synthesizing 2D materials at low temperatures on various substrates<sup>34</sup>. In 2D FETs utilizing high-κ dielectrics, the importance of smooth surfaces escalates as devices become thinner, to prevent dielectric disorder<sup>154</sup>. Consequently, planarization – a process designed to create uniform, ultra-smooth and defect-free surfaces – is crucial in the semiconductor industry. It enhances lithography and etch yields, mitigates step coverage issues, prevents electromigration, reduces contact resistances and addresses metallization challenges<sup>155</sup>.

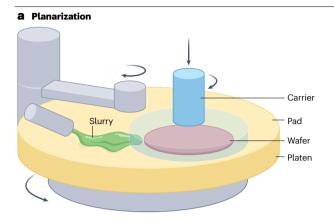

Currently, chemical mechanical polishing (CMP) is the most widely used planarization technique, achieving ultra-smooth and flat surfaces by combining mechanical forces with chemical reactions<sup>156</sup>. CMP involves pressing the substrate against a rotating polishing pad and applying a polishing slurry, as illustrated in Fig. 4a. This slurry, consisting of chemicals and abrasives, facilitates chemical reactions and, together with the controlled hardness and force applied to the substrate, effectively removes material  $^{157}$ . The composition of the slurry abrasives, corrosion inhibitors, complexing agents, pH regulators, and dispersants or surfactants - is tailored to the materials being removed<sup>158</sup>. The interaction of the slurry with different materials at the substrate interface requires careful studies. Determining the optimal material removal rate involves analysing factors such as slurry composition, mechanical force, pad texture and hardness, heat generation and platen rotation velocity<sup>159</sup>. Various models have been developed to analyse wafer-pad contact, lubrication and the chemical reactions between the slurry and metals or dielectrics to prevent defects such as metal dishing, oxide erosion and corrosion 160-162. Thermal models address issues such as metal film delamination caused by heat during CMP<sup>163-165</sup>. At present, research focuses on reducing defects, developing CMP fill synthesis 166-168, improving post-CMP cleaning methods and creating environmentally friendly slurries<sup>169</sup>. With advances in 2D electronics, testing new materials for semiconducting channels, dielectrics, contacts, vias and interconnects becomes crucial. This emphasizes the need for refined CMP methodologies for 3D ICs based on 2D electronics, requiring thorough analysis of chemical and mechanical interactions at the wafer interfaces<sup>145</sup>.

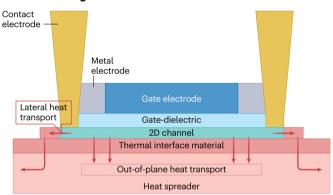

### Thermal management

Planar 2D ICs utilize bulk Si, thermal interface materials and heat sink structures for efficient thermal management<sup>170,171</sup>. However, for 3D ICs, the increased device and power density leads to higher heat generation. This issue is compounded by the difficulty of accessing and creating adequate thermal dissipation paths in the upper tiers, exacerbating the impact of heat. Exposure to higher temperatures can cause signal delays and accelerate ageing, thereby reducing the chip's lifetime. Therefore, it is crucial that every design step for a 3D IC incorporates thermal considerations. Effective heat dissipation from thermal hotspots in a 3D IC requires materials with high thermal conductivity and thermal vias or pathways that have a low overall thermal resistance, including at material interfaces. The challenges of thermal management with 2D materials are illustrated in Fig. 4b.

### **b** Thermal management

#### C Electrostatic coupling and interconnects

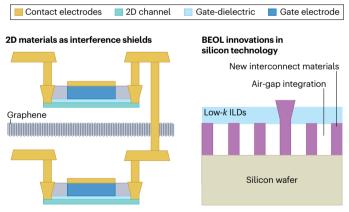

Fig. 4 | Design considerations and challenges for 3D integration with 2D electronics. a, Schematic of a typical chemical mechanical polishing setup consisting of rotating polishing pads, chemical slurry and so on with a wafer carrier. b, Thermal management challenges associated with 2D materials. They include high out-of-plane thermal insulation of 2D materials and integration obstacles for heat spreaders. c, Electrostatic coupling and interconnects. 2D materials like graphene can potentially be incorporated as barriers to prevent electrostatic interference. Since 2D-based 3D integration can potentially decrease the tier thickness considerably, it is important to keep up with the latest innovations in silicon technology such as back-side power delivery networks, air-gap integration, low- $\kappa$  interlayer dielectrics (ILDs) and the introduction of new interconnect materials, which may be adopted for 2D electronics. BEOL, back-end-of-line.

Understanding nanoscale thermal transport in 2D FETs often requires advanced theoretical models alongside experimental research<sup>172,173</sup>. Studies have explored localized heat generation in 2D electronics<sup>174</sup>, high thermal isolation between van der Waals layers<sup>175</sup>, and the effect of thermal expansion coefficient mismatch between 2D materials and substrates <sup>176,177</sup>. However, in some cases, the use of 2D materials demands new characterization techniques<sup>178</sup>. For example, in a recent study, a purely experimental approach to extract the in-plane thermal expansion coefficient of 2D TMD monolayers was presented, thereby addressing the large discrepancies in 2D TMD thermal expansion coefficient values in the literature<sup>179</sup>. In their approach. they utilized Raman spectroscopy to capture the difference in thermal expansion of the 2D material on different substrates caused by the thermal mismatch between the 2D film and the substrate to extract the thermal expansion coefficient. There are also other approaches, using van der Waals materials for both thermal isolation as well as heatspreading applications. For example, an interesting study reported extremely anisotropic thermal conductors with a room-temperature thermal anisotropy ratio – the ratio of thermal conductivity along the fast axis to that of the slow axis – of 900 for MoS<sub>2</sub> (ref. 180), suggesting that interlayer rotation may be an effective technique to engineer anisotropic thermal properties in 2D materials. Furthermore, graphene and related materials have been shown to be effective heat spreaders, potentially replacing traditional heavier materials such as aluminium and copper<sup>181,182</sup>. These experimental studies are propelling the field towards a more thermal-focused research on 2D VLSI chips. This includes the development of thermally conductive vias, spreaders, heat sinks, microfluidic channels, and other design and packaging solutions for 3D integration of 2D electronics. Various results and techniques mentioned above must be coupled with models and studies of densely integrated chips.

#### Parasitic capacitance

The impact of parasitic capacitance and electrostatic coupling between conductive elements must be carefully considered in the physical design of 3D ICs, because these can lead to detrimental effects such as signal degradation or delay, noise and crosstalk 183,184. At the device level, these electricalf interferences can cause unwanted changes in threshold voltage and increased power consumption 149,185. Therefore, during the layout stage, the routing, placement and spacing between various components should be meticulously analysed to account for capacitive coupling. This analysis necessitates the use of appropriate low- $\kappa$  dielectric materials, shielding layers and grounding planes <sup>186,187</sup>. However, considerations must also extend to interface properties, thermal conductivity and the coefficient of thermal expansion when selecting materials. Additionally, 2D materials, such as graphene, have been proposed as electrostatic screening layers (Fig. 4c). To enhance the screening efficiency of graphene, even at high-frequency regimes (up to 500 GHz), doping has been proposed, based on evaluations of its electrostatic screening properties<sup>50</sup>. Continuous innovations in silicon technology - including interconnects, power delivery and interlayer dielectrics - remain essential because they are likely to be integrated with 2D electronics in the future.

### **Architectural design considerations**

After determining the desired devices, functionalities, corresponding materials and associated fabrication processes, identifying the optimal integration approach becomes the subsequent crucial step. This requires a comprehensive electrical-design-automation tool flow

to ensure seamless incorporation while upholding the performance standards of the 3D IC  $^{188}$ . A primary step towards 3D integration is tier partitioning, which involves dividing the 3D IC into distinct tiers based on functionality, fabrication processes, power delivery and thermal management. This division can occur at the transistor level, the block level or the gate level.