Abstract

This study examines the operational parameters of field-effect transistors (FETs) using single-gate (SG) and double-gate (DG) graphene nanoribbons (GNRs) within the analog/RF domain. A detailed exploration is conducted through an atomistic pz orbital model, derived from the Hamiltonian of graphene nanoribbons, employing the nonequilibrium Green’s function formalism (NEGF) for analysis. The atomic characteristics of the GNRFETs channel are accurately described by utilizing a tight-binding Hamiltonian with an atomistic pz orbital basis set. The primary focus of the analysis revolves around essential analog/RF parameters such as transconductance, transconductance generation factor (TGF), output resistance, early voltage, intrinsic gain, gate capacitance, cut-off frequency, and transit time. Furthermore, the study assesses the gain frequency product (GFP), transfer frequency product (TFP), and gain transfer frequency product (GTFP) to evaluate the balance between transistor efficiency, gain, and cut-off frequency. The research outcomes indicate that double-gate GNRFETs exhibit superior analog/RF performance in comparison to their single-gate counterparts. However, both types of devices demonstrate cut-off frequencies in the gigahertz range. The extensive data presented in this study provides valuable insights into the characteristics of SG and DG GNRFETs, particularly in terms of the figure-of-merit (FoM) for analog/RF performance, offering a comprehensive analysis of the trade-offs in analog applications. In addition, the analysis has been extended be performing a high-performance hybrid 6T static random-access memory (SRAM) to get the impact in their circuit level variation as well as improvement in their circuit performance.

Similar content being viewed by others

Introduction

In recent years, there has been a significant reduction in the size of transistors, transitioning from the micrometer to the nanometer scale in line with Moor’s Law1,2. Despite this progress, the increasing demand for advanced electronic devices has posed substantial challenges to the limitations of silicon-based transistors in terms of size. The primary challenges include short-channel effects (SCE), parameter fluctuations due to parasitic impacts, process variations, and dopant randomness. Researchers have actively engaged in exploring alternative materials to address these limitations. Graphene has emerged as a prominent candidate due to its widespread availability and cost-effectiveness3.

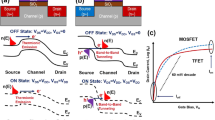

Graphene, a single-layered carbon atom structure, has garnered attention for its exceptional properties, making it a compelling material for the future generation’s semiconductor devices. These properties include remarkable thermal conductivity, high saturation velocity, flexibility, robust mechanical strength, and high carrier mobility4,5,6,7,8. Graphene’s outstanding mobility characteristics make it particularly suitable for applications in flexible and radio frequency (RF) devices9,10. Additionally, its ambipolar transport characteristics offer unique advantages for electronic device applications11,12. Nevertheless, graphene nanoribbons (GNRs) exhibit greater promise compared to graphene, given that the latter is a material with zero bandgap, making it unsuitable for switching applications. GNRs, which are elongated cut-out strips of graphene sharing electronic characteristics with semi-infinite graphene sheets, are generally presumed to possess finite nanometer dimensions. The bandgap of GNRs can be deliberately manipulated, presenting them as potential candidates for nano-electronic devices. Utilizing advanced patterning techniques like e-beam lithography, a slender strip of one-dimensional GNRs can be crafted from a 2D graphene monolayer13,14,15,16,17. GNRs come with two primary edge shapes—armchair GNRs (AGNRs) and zigzag GNRs (ZGNRs)—depending on their edge orientation. ZGNRs consistently exhibit metallic properties, while AGNRs can be categorized into three families: 3p, 3p + 1, and 3p + 2. The 3p and 3p + 1 families act as semiconductors, while the 3p + 2 family displays metallic characteristics. The bandgap significantly influences the performance metrics of devices, underscoring the crucial role of a band structure approach in the design and manufacturing of nanoelectronics18. Typically, the GNR-FET represents a standard field-effect transistor (FET) device in which a GNR channel is incorporated between the drain and the source. The channels within GNR-FETs exhibit remarkable sensitivity, making them applicable across a broad spectrum of practical uses. What sets GNR-FETs apart from conventional FET technologies is their distinctive switching capability between p and n channels19. It has been observed that the subtle unintentional doping in graphene samples, resulting from the deposition of the top-gate stack, counteracts the compact nature of the device20. Some researchers have determined the mobility of charge carriers, considering the minimal carrier concentration in a specific channel based on its length. Consequently, they strongly advocate for the GNR-FET as a promising alternative in the post-Silicon era of the semiconductor industry21. Following extensive research, top-gated GNR-FETs with a mobility range of 6000–7000 cm2 V−1 s−1 have been developed by optimizing the high-k dielectric material. Notably, the mobility of GNR-FETs surpasses that of traditional Si-based FET devices22,23,24. Additionally, reports indicate that the transconductance and transit frequency of GNR-FETs exhibit higher values compared to those of similarly sized CMOS structures25. Consequently, the GNR-FET holds tremendous potential in the field of microwave and radio frequency (RF) devices.

As electronic devices continue to shrink into the nanometer range, maintaining satisfactory analog/RF performance parameters while minimizing power consumption poses an escalating challenge26. Recent studies have delved into assessing the analog/RF performance of graphene nanoribbon field-effect transistors, exploring the impact of diverse factors on these parameters. These factors encompass distinct dielectrics27, gate length, gate oxide material, and gate oxide thickness28, along with considerations of the underlap effect29 and vacancy defects30. Another avenue to enhance analog/RF performance involves the adoption of triple-material gates31. Nevertheless, there remains considerable room for further research to optimize analog/RF parameters, and the capability to interchange and fine-tune these parameters is crucial in analog circuit design to pinpoint the most suitable operating region. To address this gap, the present study focuses on applying this approach to graphene-based devices, scrutinizing the performance of both single-gate (SG) GNR-FET and double-gate (DG) GNR-FET. This analysis includes a comprehensive assessment of the trade-off between transistor efficiency and unit frequency gain, detailed in this article.

This study aims to bridge this research gap by examining the various analog and RF performance parameters of GNR-FETs. Subsequently, a comparison is drawn between the optimized single-gate and double-gate GNR-FET devices in terms of various analog/RF performance parameters. To conduct the trade-off analysis of the doped contact GNR-FETs, an in-depth quantum transport method is employed, utilizing the nonequilibrium Green's function (NEGF) formalism. This approach effectively addresses the Schrödinger equation in conjunction with a two-dimensional Poisson's equation within real space, ensuring self-consistency. The NEGF formalism is widely accepted and extensively used for simulating nano-electronic devices, recognized for its notable conformity with experimental outcomes compared to semiclassical methods32. The investigation encompasses a range of analog/RF parameters, including transconductance, transconductance generation factor (TGF), output resistance, intrinsic gain, early voltage, gate capacitance, cut-off frequency, transfer frequency product (TFP), gain frequency product (GFP), and gain transfer frequency product (GTFP) for both single-gate and double-gate GNR-FETs. Results show DG GNR-FETs offer improved electrostatic control, mitigating SCEs, exhibiting superior transconductance, efficiency, frequency response, and wider frequency range operation. To explore the utilization of the suggested GNR-FET devices, we have designed a hybrid 6T static random-access memory (SRAM) cell incorporating this technology. The performance of this hybrid SRAM is optimized by varying the capacitance at the source-channel junction of GNR-FETs, while ensuring other device performance metrics remain unaffected. Subsequently, a comparative analysis has been conducted, evaluating the performance of the hybrid 6T-SRAM against conventional SG GNR-FETs and DG GNR-FETs-based 6T-SRAM designs.

Device structure and simulation methodology

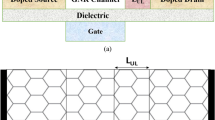

The simulated n-i-n type single-gate and double-gate device structures, depicted in Fig. 1a,b respectively, consist of a 12-AGNR serving as the channel material, with a band gap of 0.6 eV. The width of GNR channel is 1.37 nm, while source, drain, and gate regions of the device have a length of 10 nm.

The Al2O3 is considered a top and bottom gate dielectric having a dielectric constant of 10. The source and drain regions are doped with the same density of 2.5 × \(10^{13}\) \({\text{cm}}^{ - 2}\) in order to achieve an n-type extension of GNR channel. In case of the double-gate GNR-FET, gate oxide has a physical thickness of 2 nm on both the top and bottom layers. However, for single-gate GNR-FET, bottom gate oxide is ten times thicker than top gate oxide thickness (2 nm) to eliminate gate effect in the device. This approach has been previously employed in33. The drain is biased at a voltage of 0.5 V, and all simulations are conducted using the atomistic device simulator NanoTCAD ViDES34 at a temperature of 300 K.

The GNR-FET simulation was conducted using the NEGF framework. The crucial aspect of the NEGF formalism involves determining the appropriate Hamiltonian for the material. The tight-binding approximation has been used for the result analysis because it provides reasonable accuracy for the material that has been used during our analysis. In addition, incorporating a pz orbital basis set further refines the model by considering a specific orbital shape and symmetries that is relevant to the electronic structure of the material. For simulation purposes, the utilized Hamiltonian is a 2-band model, and it can be expressed as follows35:

the parameters EA and EB indicate the energy levels situated at the uppermost point of the valence band and the lowermost point of the conduction band, respectively. These parameters are related by the equation EB − EA = EG, where EG denotes the bandgap. The tight-binding Hamiltonian matrix is utilized in the 1-D real space basis of the elementary cell, possesses a value of lateral hopping energy, t = − 2.7 eV36,37.

the f(k) is expressed as38:

where a1 and a2 are the primitive lattice vectors.

Once the Hamiltonian matrix is defined, the next step involves calculating the Green's function, as shown in39:

To incorporate the influence of the source and drain contacts, corresponding self-energy matrices \(\sum_{S}\) and \(\sum_{D}\) are added to the Hamiltonian matrix. The self-energies for the Green’s function are determined through a recursive relation40. The computation of the retarded Green’s function involves applying Gaussian elimination to both the Hamiltonian matrix and the self-energy matrices. This allows us to find the charge density on atomic sites for different ky values using the retarded Green's function, following a similar approach as described in reference41. To discretize and solve the partial differential equations (PDEs), numerical methods such as finite difference method has been approximated by the simulator. The quantum mechanical effects such as tunneling and ballistic transport are being taken care by the Non-Equilibrium Green's Function. To determine the charge density, a self-consistent equation is solved alongside the 2-D Poisson equation. The calculations are repeated iteratively until a specific convergence criterion is met. The finite difference method is used to handle the 2-D Poisson equation in the xz plane. Within this iterative inner nonlinear loop, which connects potential energy to charge density, the Newton–Raphson method is utilized42. Once convergence is achieved, the source- to-drain current is calculated by evaluating the transmission function through the Landauer formula39.

Results and discussion

Before initiating the analysis of GNR-FETs with different structure, the accuracy of the current simulator is assessed. To achieve this, a simulation is conducted based on a previous study43, focusing on n-i-n GNR-FET devices. The results are depicted in Fig. 2, highlighting the excellent agreement between our simulations and the findings reported in the referenced article.

ID–VGS characteristics of the simulator and reported43 data.

After confirming the accuracy of our simulation, we employed the previously explained approach to determine the drain current by varying VGS, as shown in Fig. 3. It is observed from Fig. 3 that the DG GNR-FET exhibits a greater ON current in contrast to that of the SG GNR-FET. The increased ON current in the DG GNR-FET compared to the SG GNR-FET can be attributed to the superior control of channel conductance by the gate in the DG structure. This enhanced control is a result of the gate’s ability to modulate the channel from both the top and bottom, effectively optimizing the flow of charge carriers through the channel. Consequently, the DG configuration provides a more efficient pathway for current to flow, leading to higher ON current levels44. When the gate voltage varies from 0 to 0.8 V of VDS, the current changes quickly; hence, the current ON/OFF ratio (ION/IOFF) is observed as 5.28 × 102 and 2.69 × 103 for SG GNR-FET and DG GNR-FET, respectively, as illustrated in Fig. 4. Here, the ON current is set at VDS = 0.5 V and VGS = 0.8 V.

Drain induced barrier lowering (DIBL) is a crucial aspect of short-channel effects and serves as a significant consideration in the design of low-power integrated circuits (ICs). As depicted in Fig. 5, it is noted that the DIBL is 220.25 mV/V for SG GNR-FETs. However, this value decreases to 53.74 mV/V for DG GNR-FETs. The higher DIBL in SG structure is due to the higher IOFF, however for the DG structure, the DIBL diminishes, leading to a decrease in IOFF.

Figure 6 illustrates conduction band profile of the device at ON state. It is observed from Fig. 6 that GNR-FET with DG structure covers lower energy path; therefore, the device with DG structure has higher ION compared to GNR-FET with SG structure. This difference in the energy band diagram can be attributed to the higher capacitance in the double gate structure, stemming from the reduced oxide thickness and the presence of two gates in close proximity, as depicted in Fig. 12. The heightened capacitance leads to increased charge inversion at saturation in Field-Effect Transistors, where the channel is fully formed, and the inversion charge reaches its peak45. Typically, the distribution of inversion capacitance is higher at the source side due to channel length modulation effects. Consequently, the elevated inversion charge induced by channel length modulation results in a more pronounced shift in the Fermi level at the source side of the double gate structure46. Figure 7 shows and transmission probability for the ON-state along device's transport length. It is observed from Fig. 7 that transmission in conduction band increases as wire thickness decreases. The ballistic current is calculated by comparing the transmission with energy. Notably, the transmission steps exhibit dependence on channel and exhibit regions of high transmission at an energy of E = 0.44 eV. The energy observed in SG and DG GNR-FETs is approximately 1.979 eV and 1.996 eV, respectively. Consequently, DG GNR-FET exhibits 1.0086 times higher transmission compared to SG GNR-FET devices.

Analog performance

Following the analysis of the transfer characteristics of the devices, this section examines the additional significant figures-of-merit (FoMs) for analog integrated circuits. These FoMs include transconductance (gm), transconductance generation factor (TGF), output conductance (gd), output resistance (r0), early voltage (VEA) and intrinsic gain (Av).

The ability of a device to amplify a signal is determined by its transconductance. A higher transconductance value indicates a greater capacity for amplification or gain. The following definitions and calculations apply to the gm, TGF and gd parameters47,48:

Figure 8 demonstrates the initial increase of gm with VGS, eventually reaching its peak value. The DG GNR-FET achieves a peak gm value of 108.92 µS, whereas the SG GNR-FET reaches a maximum value of 68.47 µS. This disparity can be attributed to the proportional relationship between gm and ID. The TGF signifies the efficient utilization of drain current to attain a desirable gm value. A higher TGF value implies that the device is suitable for amplifier designs, especially in situations requiring low power. Figure 5 illustrates the variation of TGF for both SG GNR-FET and DG GNR-FET. It is observed that the maximum TGF value is attained at low VGS, but degrades significantly as VGS increases, indicating a high gain with minimal power dissipation. Figure 9 illustrates the plot of r0 and gd as VGS varies. The results demonstrate that both the considered devices exhibit a decrease in r0 and an increase in gd. However, the SG GNR-FET achieves a higher maximum output resistance compared to the DG GNR-FET. Conversely, the DG GNR-FET attains a higher maximum gd value compared to the SG GNR-FET. A larger gd value indicates a superior conversion efficiency from drain current to drain voltage.

The intrinsic gain and early voltage can be determined as46,48:

Figures 10 and 11 illustrate the relationship between VEA and VGS, as well as the Av relation with respect to VGS, respectively. These relationships are determined by Eqs. (7) and (8) respectively. To achieve better analog performance, it is desirable to have higher values of VEA and Av. It can be observed from Fig. 10 that the maximum value of VEA is obtained with DG GNR-FET. Consequently, the Av, which is the product of gm and r0, is primarily influenced by r0 at both low VGS and high VGS. As a result, the maximum value of Av is attained with DG GNR-FET, as illustrated in Fig. 11.

RF performance

This section focuses on conducting an analysis of the RF performance for both SG and DG GNR-FET devices. When it comes to RF analysis, the two primary FoMs considered are the gate capacitance (CG) and cut-off frequency (fT).

The gate capacitance of the device is crucial when dealing with RF applications. It is determined by calculating the ratio of the change in the concentration of charge carriers to the change in voltage46. Figure 12 depicts the gate capacitance (CG) for both SG and DG GNR-FET devices. The DG GNR-FET has a peak CG value of 2.08 fF, while the SG GNR-FET has a peak value of 1.45 fF. The ION/CG plot is depicted in Fig. 12. A greater ION/CG ratio indicates a faster switching operation in the device. Additionally, it is noted that the highest ION/CG ratio occurs at low VGS, but as VGS increases, the ION/CG ratio decreases significantly.

In RF applications, the cut-off frequency (fT = gm / 2π CG) is an important FoM for a device. It is the frequency at which the current gain reaches unity and is shown in Fig. 13. According to the equation, a device with a higher gm by CG value will result in a larger cut-off frequency. As a result, the DG GNR-FET exhibits a sharper cut-off frequency compared to the SG GNR-FET.

The transit time (τ = 1/2π fT) is an important factor to consider in RF analysis49. The transit time represents the duration required for charge carriers to move from the source to the channel. The variation of τ with respect to VGS is illustrated in Fig. 14. It can be observed from the figure that the τ value decreases for both SG and DG GNR-FETs. This decrease in τ is attributed to the higher fT of the device, which is desirable for enhanced switching performance.

The design of analog circuits requires careful consideration of the relationship between device efficiency, intrinsic gain, and bandwidth. Determining the optimal operating point involves a trade-off analysis that takes into account parameters such as transconductance frequency product (TFP), gain frequency product (GFP), and gain transconductance frequency product (GTFP)48,50. The complexity arises from the diverse factors influencing these parameters, including transistor construction, circuit design, and external elements. The relationships between these factors are nonlinear and interdependent, posing challenges in optimization. Balancing conflicting objectives, such as maximizing gain while maintaining efficiency, requires a deep understanding of semiconductor physics and optimization techniques, often involving iterative processes.

TFP is calculated by multiplying the TGF and frequency (fT) and captures the trade-off between power and bandwidth in moderate to high-speed circuit designs51. A higher TFP value allows the circuit designer to fine-tune the device's performance by adjusting the trade-off between transconductance and cut-off frequency. Figure 14 shows the plot of TFP as a function of VGS. It is observed that the DG GNR-FET exhibits a higher TFP value compared to the SG GNR-FET. The GFP represents the trade-off between gain and frequency, particularly in high-frequency applications of operational amplifiers48. The GFP is the product of intrinsic gain and fT. Figure 15 displays the plot of GFP as a function of VGS. Both the SG GNR-FET and DG GNR-FET show a high TFP value at low VGS, but this value decreases as VGS increases. However, the DG GNR-FET device reaches a higher peak value compared to the SG GNR-FET device.

Figure 16 shows the plot of GTFP as a function of VGS. It is observed from Fig. 16 that the DG GNR-FET exhibits a higher GTFP value compared to the SG GNR-FET. The GTFP is a figure of merit that indicates the performance of an amplifier in terms of gain, transistor efficiency and frequency response. This provides the circuit designer with the flexibility to select the optimal operating region by balancing factors such as gain, transconductance, and speed.

Analysis of 6T-SRAM cell design

The Fig. 17 demonstrates the widely used and basic design of a symmetric six-transistor (6T) structure, which serves as the fundamental topology for CMOS SRAM cells. At the heart of this structure are two interconnected inverters which retain a distinct logical state in the Q and \({\overline{\text{Q}}}\) nodes. These nodes can be interacted with either ‘read’ or ‘written to’ by using the bit-lines (BLs) via the access transistors (ATs), contingent upon the signal from the word-line (WL). Otherwise, the voltage levels at nodes Q and \({\overline{\text{Q}}}\) remain constant during the hold state.

The stability of SRAM is commonly assessed through its static noise margin (SNM), which indicates the maximum level of noise voltage at the inverters output that the SRAM can withstand without altering the memory cell’s contents. SNM is graphically determined from the butterfly curves of the SRAMs. It is defined as the minimum length of the sides of the two largest squares that can fit within the two lobes of the butterfly curve, as illustrated in Fig. 18. Figure 18 demonstrates that the hold SNM is superior in DG SRAM compared to conventional SRAM based on SG. This improvement in hold SNM is attributed to the rapid output transition in the hybrid SRAMs.

Conclusion

This paper focuses on evaluating the impact of single-gate (SG) and double-gate (DG) structures on the analog/RF figures-of-merit (FoMs) of graphene nanoribbon field-effect transistors (GNR-FETs). The research demonstrates that the double-gate structure exhibits significantly superior analog/RF figures-of-merit (FoMs) compared to the single-gate structure. The DG GNR-FET demonstrates a current ON/OFF ratio that is 409% higher than the SG GNR-FET. Additionally, the transconductance, transconductance generation factor, and intrinsic gain of the DG GNR-FET are 59.1%, 26.2%, and 197% superior to those of the SG GNR-FET, respectively. The study also reveals significant changes in RF FoMs. The cut-off frequency of the DG GNR-FET device is 11.4% higher than that of the SG GNR-FET device. Furthermore, the TFP, GFP and GTFP are 43.7%, 23.5% and 17.5% higher, respectively, compared to the SG device structure. These improvements can be attributed to the superior electrostatic control of the channel provided by the double-gate structure. These results hold significant value for the design of nanoscale devices intended for high-frequency applications. Based on these findings, it is suggested that the DG GNR-FET structure is more prominent when considering the analog/RF performance evaluation of the device.

Data availability

The data that support the findings of this study are available from the corresponding author, [akram14407@gmail.com], upon reasonable request.

References

Ferain, I., Colinge, C. & Colinge, J. P. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479, 310–316. https://doi.org/10.1038/nature10676 (2011).

Assad, F., Ren, Z., Vasileska, D., Datta, S. & Lundstrom, M. On the performance limits for Si MOSFETs: A theoretical study. IEEE Trans. Electron Devices 47(1), 232–240. https://doi.org/10.1109/16.817590 (2000).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306(5696), 666–669. https://doi.org/10.1126/science.1102896 (2004).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6(3), 183–191. https://doi.org/10.1038/nmat1849 (2007).

Rumyantsev, S. et al. Electrical and noise characteristics of graphene field-effect transistors: Ambient effects, noise sources and physical mechanisms. J. Phys. Condens. Matter 22(39), 395302. https://doi.org/10.1088/0953-8984/22/39/395302 (2010).

Palacios, T., Hsu, A. & Wang, H. Applications of graphene devices in RF communications. IEEE Commun. Mag. 48(6), 122–128. https://doi.org/10.1109/MCOM.2010.5473873 (2010).

Schwierz, F. Graphene transistors. Nat. Nanotechnol. 5, 487–496. https://doi.org/10.1038/nnano.2010.89 (2010).

Du, X. et al. Approaching ballistic transport in suspended graphene. Nat. Nanotechnol. 3, 491–495. https://doi.org/10.1038/nnano.2008.199 (2008).

Kim, S. et al. Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric. Appl. Phys. Lett. 94(6), 062107. https://doi.org/10.1063/1.3077021 (2009).

Novoselov, K. S. et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature 438(7065), 197–200. https://doi.org/10.1038/nature04233 (2005).

Lin, Y. M. et al. 100-GHz transistors from wafer-scale epitaxial graphene. Science 327(5966), 662. https://doi.org/10.1126/science.1184289 (2010).

Wang, H., Nezich, D., Kong, J. & Palacios, T. Graphene frequency multipliers. IEEE Electron Device Lett. 30(5), 547–549. https://doi.org/10.1109/LED.2009.2016443 (2009).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6, 183–191. https://doi.org/10.1142/9789814287005_0002 (2007).

Novoselov, K. et al. Electronic properties of graphene. Phys. Status Solidi 244, 4106–4111. https://doi.org/10.1002/pssb.200776208 (2007).

Ando, T. The electronic properties of graphene and carbon nanotubes. NPG Asia Mater. 1, 17–21. https://doi.org/10.1038/asiamat.2009.1 (2009).

Ravi, S. K. & Tan, S. C. Progress and perspectives in exploiting photosynthetic biomolecules for solar energy harnessing. Energy Environ. Sci. 8, 2551–2573. https://doi.org/10.1039/C5EE01361E (2015).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669. https://doi.org/10.1126/science.1102896 (2004).

Ravi, S. K. et al. Emerging role of the band-structure approach in biohybrid photovoltaics: A path beyond bioelectrochemistry. Adv. Funct. Mater. 28, 1705305. https://doi.org/10.1002/adfm.201705305 (2018).

Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314. https://doi.org/10.1126/science.1171245 (2009).

Moon, J. S. et al. Ultra-low resistance ohmic contacts in graphene field effect transistors. Appl. Phys. Lett. 100(20), 203512. https://doi.org/10.1063/1.4719579 (2012).

Thiele, S. A. et al. Modeling of graphene metal-oxide-semiconductor field-effect transistors with gapless large-area graphene channels. J. Appl. Phys. 107(9), 094505. https://doi.org/10.1063/1.3357398 (2010).

Liao, L. et al. Top-gated graphene nanoribbon transistors with ultrathin high-k dielectrics. Nano Lett. 10(5), 1917–1921. https://doi.org/10.1021/nl100840z (2010).

Hosen, K., Islam, M. R. & Liu, K. Impact of channel length and width for charge transportation of graphene field effect transistor. Chin. J. Chem. Phys. 33, 757–763. https://doi.org/10.1063/1674-0068/cjcp2004055 (2020).

Liao, L. et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 467, 305–308. https://doi.org/10.1038/nature0940 (2010).

Rodriguez, S. et al. RF performance projections of graphene FETs vs. silicon MOSFETs. ECS Solid State Lett. 1(5), 39–41. https://doi.org/10.1149/2.001205ssl (2012).

Afacan, E. & Dündar, G. Inversion coefficient optimization assisted analog circuit sizing tool. In 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD) 1–4 (2017). https://doi.org/10.1109/SMACD.2017.7981579.

Akbari, M. et al. A novel graphene nanoribbon field effect transistor with two different gate insulators. Physica E Low-dimens. Syst. Nanostruct. 66, 133–139. https://doi.org/10.1016/j.physe.2014.10.021 (2015).

Anvarifard, M. K. Non-linearity and RF intermodulation distortion check of ultrascale GNRFET device using NEGF technique to achieve the highest reliable performance. ECS J. Solid State Sci. Technol. 10(10), 101002. https://doi.org/10.1149/2162-8777/ac2913 (2021).

Alam, M. S., Barik, A. & Armstrong, G. A. Investigations of analog/RF performance for underlap graphene nano-ribbon field effect transistor (GNRFET). IEEE Nanotechnol. Mater. Devices Conf. (NMDC) https://doi.org/10.1109/NMDC.2012.6527600 (2012).

Nazari, A., Faez, R. & Shamloo, H. Modeling comparison of graphene nanoribbon field effect transistors with single vacancy defect. Superlattices Microstruct. 97, 28–45. https://doi.org/10.1016/j.spmi.2016.06.008 (2016).

Rao, S. S. et al. Analog/RF performance of triple material gate stack-graded channel double gate-junctionless strained-silicon MOSFET with fixed charges. Silicon 14, 7363–7376. https://doi.org/10.1007/s12633-021-01462-0 (2021).

Marian, D. et al. Multi-scale simulations of two dimensional material based devices: The NanoTCAD ViDES suite. J. Comput. Electron. https://doi.org/10.1007/s10825-023-02048-2 (2023).

Fiori, G., Iannaccone, G. & Klimeck, G. A three-dimensional simulation study of the performance of carbon nanotube field-effect transistors with doped reservoirs and realistic geometry. IEEE Trans. Electron Devices 53(8), 1782–1788. https://doi.org/10.1109/TED.2006.878018 (2006).

NanoTCAD ViDES. [Online] (2020). Available: http://vides.nanotcad.com/vides

Lovarelli, G., Calogero, G., Fiori, G. & Iannaccone, G. Multiscale pseudoatomistic quantum transport modeling for van der Waals heterostructures. Phys. Rev. Appl. 18, 034045. https://doi.org/10.1103/PhysRevApplied.18.034045 (2022).

Son, Y.-W. et al. Energy gaps in graphene nanoribbons. Phys. Rev. Lett. 97(21), 216803. https://doi.org/10.1103/PhysRevLett.97.216803 (2006).

Fiori, G. & Iannaccone, G. Multiscale modeling for graphene-based nanoscale transistors. Proc. IEEE 101(7), 1653–1669. https://doi.org/10.1109/JPROC.2013.2259451 (2013).

Aliofkhazraei, M., et al., Graphene Science Handbook Nanostructure and Atomic Arrangement (CRC Press Inc., 2016). ISBN: 9781466591370-CAT# K20510.

Datta, S. Nanoscale device modeling: The Green’s function method. Superlattice Microstruct. 28(4), 253–278. https://doi.org/10.1006/spmi.2000.0920 (2000).

J. Guo, Carbon Nanotube Electronics: Modeling, Physics, and Applications, Ph.D. dissertation (Department of Electrical Engineering, Purdue University, 2004).

Ouyang, Y., Yoon, Y. & Guo, J. Scaling behaviors of graphene nanoribbon FETs: A three-dimensional quantum simulation study. IEEE Trans. Electron Devices 54(9), 2223–2231 (2007).

Z. Ren, “Nanoscale MOSFETs: Physics, simulation and design,” Ph.D. dissertation, Dept. Elect. Eng., Purdue Univ., West Lafayette, IN, USA, Dec. 2001.

Yoon, Y., Fiori, G., Hong, S., Iannaccone, G. & Guo, J. Performance comparison of graphene nanoribbon FETs with Schottky contacts and doped reservoirs. IEEE Trans. Electron Devices 55(9), 2314–2323. https://doi.org/10.1109/TED.2008.928021 (2008).

Sarvari, H., Ghayour, A., Chen, Z. & Ghayour, R. Analyses of short channel effects of single-gate and double-gate graphene nanoribbon field effect transistors. J. Mater. 2016, 1–8. https://doi.org/10.1155/2016/8242469 (2016).

Hu, C., MOS Capacitor (University of California, 2020/01). https://www.chu.berkeley.edu/wp-content/uploads/2020/01/Chenming-Hu_ch5-1.pdf.

Mech, B. C., Koley, K. & Kumar, J. The understanding of SiNR and GNR TFETs for analog and RF application with variation of drain-doping molar fraction. IEEE Trans. Electron Devices 65(10), 4694–4700. https://doi.org/10.1109/TED.2018.2867443 (2018).

Kumar, B., Sharma, M. & Chaujar, R. Junctionless-accumulation-mode stacked gate GAA FinFET with dual-k spacer for reliable RFIC design. Microelectron. J. 139, 105910. https://doi.org/10.1016/j.mejo.2023.105910 (2023).

Mohapatra, S. K. et al. Estimation of analog/RF figures-of-merit using device design engineering in gate stack double gate MOSFET. Mater. Sci. Semicond. Process. 31, 455–462. https://doi.org/10.1016/j.mssp.2014.12.026 (2015).

Singh, P. & Yadav, D. S. Performance analysis of ITCs on analog/RF, linearity and reliability performance metrics of tunnel FET with ultra-thin source region. Appl. Phys. A 128(7), 612. https://doi.org/10.1007/s00339-022-05741-4 (2022).

Mohapatra, S. K., Pradhan, K. P., Sahu, P. K. & Kumar, M. R. The performance measure of GS-DG MOSFET: An impact of metal gate work function. Adv. Nat. Sci. Nanosci. Nanotechnol. 5(2), 6. https://doi.org/10.1088/2043-6262/5/2/025002,025002 (2014).

Pradhan, K. P. et al. Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron. J. 45(2), 144–151. https://doi.org/10.1016/j.mejo.2013.11.016 (2014).

Author information

Authors and Affiliations

Contributions

M.A.A.: Analysis, writing—original draft. P.K.: Analysis, conceptualization. B.C.M.: Methodology, supervision. J.K.: Conceptualization, supervision.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ahmad, M.A., Kumar, P., Mech, B.C. et al. Trade-off analysis between gm/ID and fT of GNR-FETs with single-gate and double-gate device structure. Sci Rep 14, 10218 (2024). https://doi.org/10.1038/s41598-024-59908-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-59908-5

Keywords

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.